Dépôt Institutionnel de l'Université libre de Bruxelles / Université libre de Bruxelles Institutional Repository

#### Thèse de doctorat/ PhD Thesis

#### Citation APA:

Verhagen, E. (2015). Development of the new trigger and data acquisition system for the CMS forward muon spectrometer upgrade (Unpublished doctoral dissertation). Université libre de Bruxelles, Faculté des Sciences – Physique, Bruxelles.

Disponible à / Available at permalink: https://dipot.ulb.ac.be/dspace/bitstream/2013/209110/4/68417d6f-4c59-4f63-a156-6c0596f70256.txt

(English version below)

Cette thèse de doctorat a été numérisée par l'Université libre de Bruxelles. L'auteur qui s'opposerait à sa mise en ligne dans DI-fusion est invité à prendre contact avec l'Université (di-fusion@ulb.be).

Dans le cas où une version électronique native de la thèse existe, l'Université ne peut garantir que la présente version numérisée soit identique à la version électronique native, ni qu'elle soit la version officielle définitive de la thèse.

DI-fusion, le Dépôt Institutionnel de l'Université libre de Bruxelles, recueille la production scientifique de l'Université, mise à disposition en libre accès autant que possible. Les œuvres accessibles dans DI-fusion sont protégées par la législation belge relative aux droits d'auteur et aux droits voisins. Toute personne peut, sans avoir à demander l'autorisation de l'auteur ou de l'ayant-droit, à des fins d'usage privé ou à des fins d'illustration de l'enseignement ou de recherche scientifique, dans la mesure justifiée par le but non lucratif poursuivi, lire, télécharger ou reproduire sur papier ou sur tout autre support, les articles ou des fragments d'autres œuvres, disponibles dans DI-fusion, pour autant que :

- Le nom des auteurs, le titre et la référence bibliographique complète soient cités;

- L'identifiant unique attribué aux métadonnées dans DI-fusion (permalink) soit indiqué;

- Le contenu ne soit pas modifié.

L'œuvre ne peut être stockée dans une autre base de données dans le but d'y donner accès ; l'identifiant unique (permalink) indiqué ci-dessus doit toujours être utilisé pour donner accès à l'œuvre. Toute autre utilisation non mentionnée ci-dessus nécessite l'autorisation de l'auteur de l'œuvre ou de l'ayant droit.

------ English Version ------

This Ph.D. thesis has been digitized by Université libre de Bruxelles. The author who would disagree on its online availability in DI-fusion is invited to contact the University (di-fusion@ulb.be).

If a native electronic version of the thesis exists, the University can guarantee neither that the present digitized version is identical to the native electronic version, nor that it is the definitive official version of the thesis.

DI-fusion is the Institutional Repository of Université libre de Bruxelles; it collects the research output of the University, available on open access as much as possible. The works included in DI-fusion are protected by the Belgian legislation relating to authors' rights and neighbouring rights. Any user may, without prior permission from the authors or copyright owners, for private usage or for educational or scientific research purposes, to the extent justified by the non-profit activity, read, download or reproduce on paper or on any other media, the articles or fragments of other works, available in DI-fusion, provided:

- The authors, title and full bibliographic details are credited in any copy;

- The unique identifier (permalink) for the original metadata page in DI-fusion is indicated;

- The content is not changed in any way.

It is not permitted to store the work in another database in order to provide access to it; the unique identifier (permalink) indicated above must always be used to provide access to the work. Any other use not mentioned above requires the authors' or copyright owners' permission.

Université Libre de Bruxelles – Faculté des Sciences IIHE – Interuniversity Institute for High Energies (ULB – VUB)

## Development of the new trigger and data acquisition system for the CMS forward muon spectrometer upgrade

## Erik Verhagen

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Science

Supervisor:

Jury:

Gilles De Lentdecker (ULB)

Kael Hanson (Président, ULB) Juanan Aguilar (Secrétaire, ULB) Frédéric Robert (ULB) Michael Tytgat (Universiteit Gent) Nick Van Remortel (Universiteit Antwerpen)

« Soumettre un nouveau à des épreuves d'initiation, avant de l'admettre au sein d'une société scolaire ou universitaire »

Définition du mot bizutage, Larousse.

## Acknowledgements

First, I would like to thank Gilles, Kael and Daniel Bertrand for making possible this four-years work contract as an electronics engineer at the Inter-university Institute for High Energies in Brussels. Thanks also to the warm welcome of Yifan in the newly created R&D group and the kindness of Danielle who helped me with the heavy administrative matters of the beginning. These key people made my initial move to Belgium in 2010 a good idea for the future.

Secondly, a number of co-students deserve special thanks too, especially Thomas L. and Alexandre, who helped until the last days with clever inputs to my work and friendly comments. The rest of the R&D team belongs also in this list, Thierry and Florian who sometimes succeeded to convince me with obscure physics explanations, and Patrizia, Valérie and Ryo for sharing their opinions during our informal group meetings.

Thanks also to the people of the *Friday beer* after-works, who helped to keep my spirit high, Thomas R. and Ludivine, Laurent T., Aidan, Thomas M. and David, not forgetting Tomislav to whom I wish especially all the best.

Last but not least, I will not forget the lovely lady who made my stay in Brussels enjoyable for the last four years, and who always believed in me, even when the mood was low. I can now tell that the strongest point I acquired during this work is perseverance, and this is thanks to her.

## **Revision History**

| Revision<br>Date         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.0<br>23/01/2015        | Initial submission for private defense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| (partial)<br>13/02/2015  | <ul> <li>Old Chapter 3.3 « Front-end signal processing » moved to Chapter 4.3 « Front-end electronics ». This chapter describes a number of preliminary studies performed in answer to the specifications set by CMS on the front-end electronics.</li> <li>New Chapter 3.3 on the physics performance of the proposed GE1/1 system describing:         <ul> <li>the goals (the physics behind)</li> <li>the muon trigger performance</li> <li>the muon reconstruction performance</li> </ul> </li> </ul>                                                                                                                               |  |  |

| (partial)<br>18/02/2015  | <ul> <li>New section 6.2.3 summarizing the results of the setup in the<br/>beam tests conducted at CERN last December</li> <li>Added list of acronyms at the end</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| (partial)<br>23/02/2015  | <ul> <li>Corrected typos and some incorrect English construction in Revision 1.0. Many thanks to Kael for spotting and reporting most of them.</li> <li>Broadened most local end-of-chapter conclusions to give a more consistent link between each individual chapters</li> <li>Added/replaced some figures in Chapter Four with more recent and explicit ones.</li> <li>Added a last paragraph in the introduction listing the contribution of my very self in this thesis, to specify where "we" should be read as "me".</li> <li>Applied some cosmetics (tale-style images in chapter intros) and added acknowledgements</li> </ul> |  |  |

| <b>2.0</b><br>26/02/2015 | Final submission for public defense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

## Contents

| INTRODUCTION                                           | 1         |

|--------------------------------------------------------|-----------|

| CHAPTER 1: The LHC and CMS: The collider and the exp   | eriment 3 |

| 1.1 Cultural background in particle physics            | 4         |

| 1.1.1 Short contextual history                         |           |

| 1.1.2 Introduction to particle accelerators            |           |

| 1.1.3 Collider experiments                             |           |

| 1.2 The LHC                                            | 8         |

| 1.2.1 Context                                          | 8         |

| 1.2.2 Key parameters of the LHC                        |           |

| 1.2.3 Upgrade plan                                     |           |

| 1.3 The Compact Muon Solenoid (CMS) detector           | 12        |

| 1.3.1 Facts and figures                                |           |

| 1.3.2 Barrel                                           |           |

| 1.3.2.1 Silicon tracker                                | 13        |

| 1.3.2.2 Electromagnetic Calorimeter (ECAL)             | 15        |

| 1.3.2.3 Hadron Calorimeter (HCAL)                      |           |

| 1.3.2.4 Superconducting solenoid                       |           |

| 1.3.2.5 Muon chambers                                  |           |

| 1.3.3 End caps                                         |           |

| 1.3.3.1 Muon chambers                                  |           |

| 1.3.3.2 Forward Calorimeter                            |           |

| 1.3.4 Upgrades                                         |           |

| 1.4 Conclusion                                         | 23        |

| CHAPTER 2: The CMS trigger and data acquisition system | 25        |

| 2.1 Basic DAQ design features                          | 26        |

| 2.2 Overview of the CMS trigger system                 | 28        |

| 2.2.1 Level-1 trigger (LV1)                            | 28        |

| 2.2.2 High Level Trigger (HLT)                         | 30        |

| 2.2.3 Muon system L1 trigger                           | 30        |

| 2.3 The CMS Data Acquisition System architecture       | 33        |

| 2.3.1 Event readout interface                          | 33        |

| 2.3.2 Event builder and filter                         |           |

| 2.3.3 Control and monitoring                           | 35        |

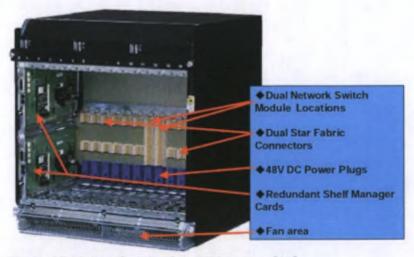

| 2.4 Har | dware implementation                     | 37 |

|---------|------------------------------------------|----|

|         | Front-end electronics                    |    |

|         | ATCA standard                            |    |

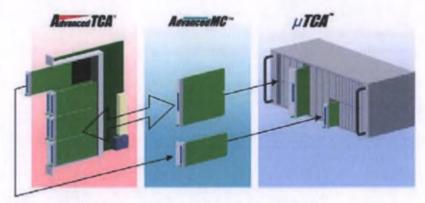

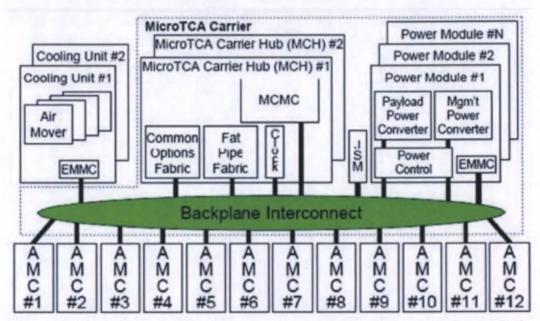

| 2.4.3   | μTCA architecture                        | 40 |

| 2.5 Con | nclusion                                 | 43 |

| CHAPTER | 3: GEM detectors and the GE1/1 system    | 45 |

| 3.1 Mu  | on system technologies comparison in CMS | 46 |

|         | Drift Tubes                              |    |

|         | Cathode Strip Chambers                   |    |

| 3.1.3   | Resistive Plate Chambers                 | 48 |

| 3.2 The | GEM detector technology                  | 50 |

| 3.2.1   | The GEM foil                             | 50 |

|         | Triple-GEM detectors                     |    |

| 3.2.3   | The GE1/1 station                        | 55 |

| 3.3 Phy | sics performance                         | 59 |

| 3.3.1   | Goals                                    | 59 |

| 3.3.2   | Muon trigger performance                 | 60 |

|         | Muon reconstruction performance          |    |

| 3.4 Cor | nclusion                                 | 66 |

| CHAPTER | 4: GE1/1 read-out system architecture    | 67 |

| 4.1 Cor | straints and requirements                | 68 |

|         | Genesis of the project                   |    |

|         | Performance requirements                 |    |

| 4.1.3   | Mechanical considerations                | 70 |

| 4.1.4   | Integration in the CSC trigger logic     | 72 |

| 4.1.5   | Technical limitations                    | 73 |

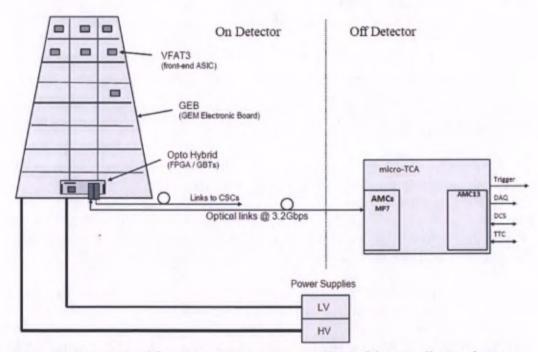

| 4.2 Sys | tem overview for LS2                     | 74 |

| 4.3 Fro | nt-end electronics                       | 76 |

| 4.3.1   | Specifications                           | 76 |

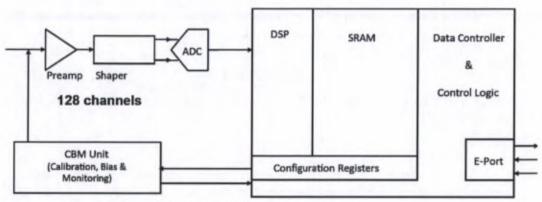

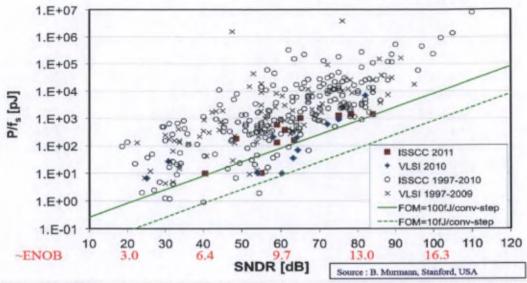

| 4.3.2   | gDSP option                              | 77 |

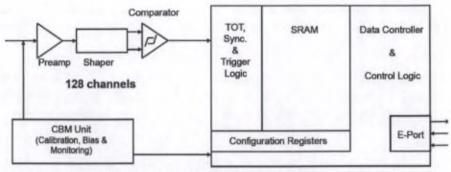

|         | VFAT3 option                             |    |

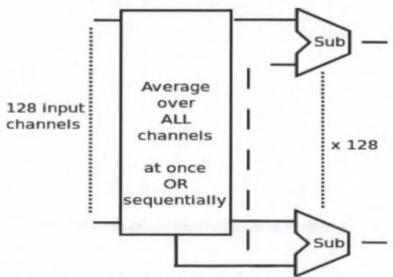

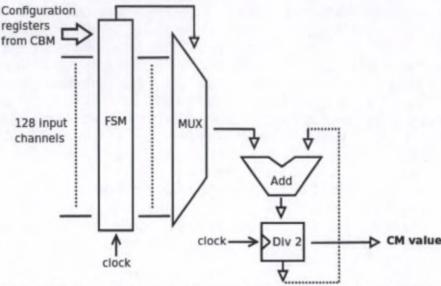

|         | Common mode reduction algorithm          |    |

|         | Time resolution improvement              |    |

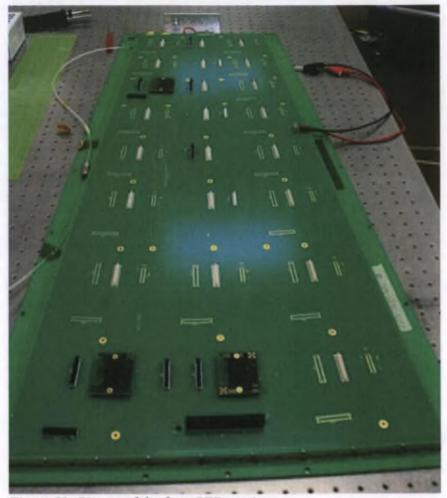

|         | The GEM Electronic Board (GEB)           |    |

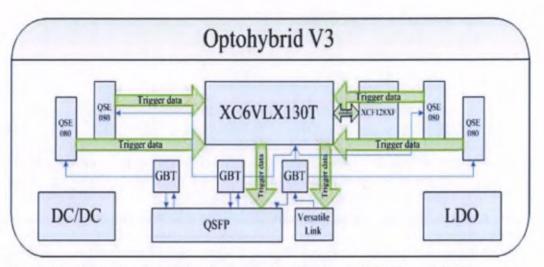

|         | The opto-hybrid                          |    |

| 4.4 Bac | k-end electronics                        | 90 |

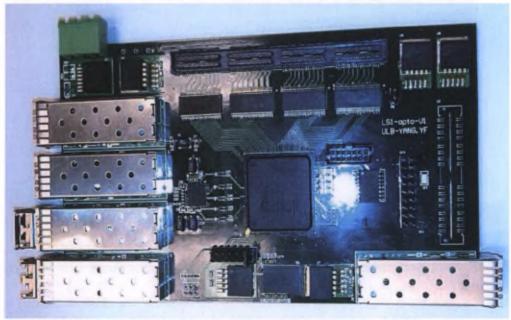

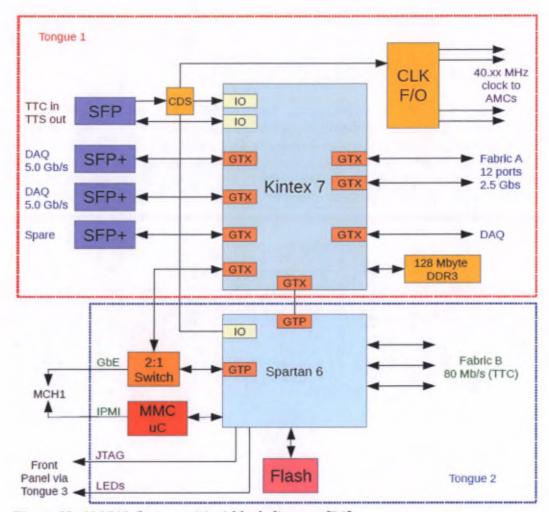

|         | μTCA based architecture                  |    |

|         | The MP7 processing boards                |    |

|         | The 13th Advanced Mezzanine Card (AMC13) |    |

|         | tem description for slice test           |    |

|         | Motivations                              |    |

| 452     | Front-end electronics                    | 95 |

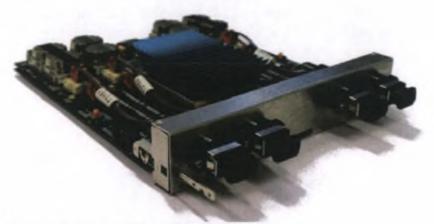

| 4.5.3   | Off-detector electronics                 | 96  |

|---------|------------------------------------------|-----|

| 4.6 Cor | nclusion                                 | 97  |

| CHAPTER | 25: μTCA developments                    | 99  |

| 5.1 μT  | CA infrastructure                        | 100 |

| 5.1.1   | The µTCA form factor                     | 100 |

| 5.1.2   |                                          |     |

|         | e-Keying and fabric interface            |     |

|         | Software integration                     |     |

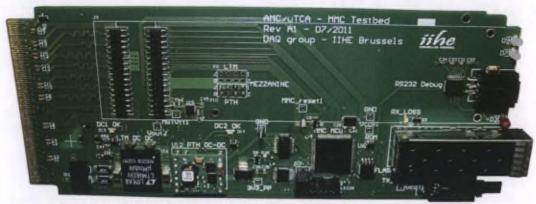

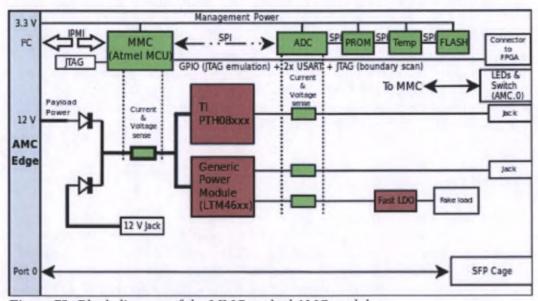

|         | dule Management Controller (MMC) testbed |     |

| 5.2.1   | Motivation                               | 103 |

| 5.2.2   |                                          |     |

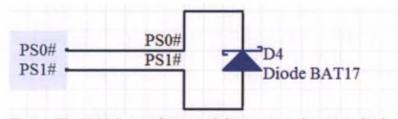

| 5.2.3   | AMC edge connector                       |     |

|         | 2.3.1 Physical characteristics           |     |

|         | 2.3.2 Power rails and presence signal    |     |

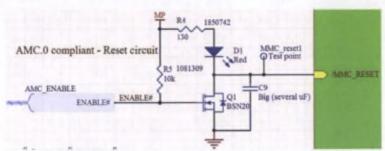

|         | 2.3.3 AMC enable signal                  |     |

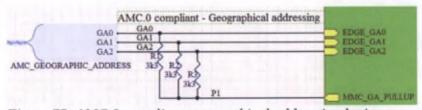

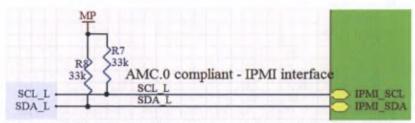

|         | 2.3.4 Geographical addressing and IPMI   |     |

|         | 2.3.5 Fabric interfaces                  |     |

|         | Power                                    |     |

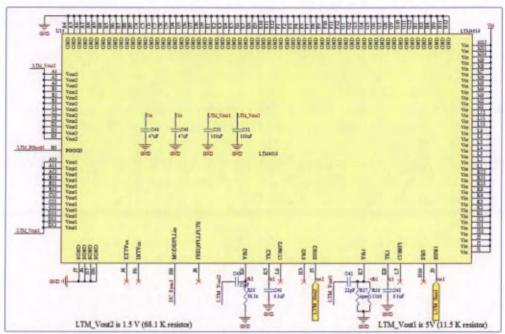

|         | 2.4.1 Input rails                        |     |

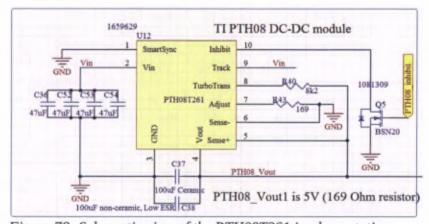

|         | 2.4.2 DC/DC converters                   |     |

|         | 2.4.3 Additional 3.3 Volt payload power  |     |

|         | 2.4.4 Low Drop-Out (LDO) regulators      |     |

|         | Module Management Controller (MMC)       |     |

|         | 2.5.1 Description                        |     |

|         | 2.5.2 Micro-controller                   |     |

|         | 2.5.3 AMC.0 compliant signals            |     |

|         | 2.5.4 AMC.0 compliant EEPROM             |     |

|         | 2.5.5 Additional FLASH memory            |     |

|         | 2.5.6 JTAG scheme                        |     |

|         | 2.5.7 User FPGA reconfiguration          |     |

|         | Monitoring and on-board network          |     |

|         | Operation and debug interface            |     |

| 5.2.8   | Fabric interface mezzanine               | 117 |

| 5.3 Ren | note firmware upgrade                    | 118 |

| 5.3.1   | Motivation                               | 118 |

| 5.3.2   | Firmware                                 | 118 |

| 5.3.3   |                                          |     |

| 5.4 Cor | nclusion                                 |     |

| CHAPTER | 6: Cosmic test-bench                     | 123 |

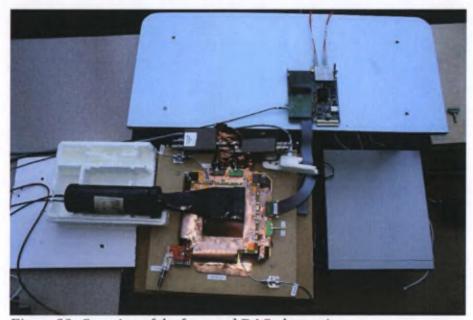

| 6.1 Exp | perimental setup                         | 124 |

|         | Triple-GEM prototype                     |     |

|         | Trigger system                           |     |

|         | DAQ electronics                          |     |

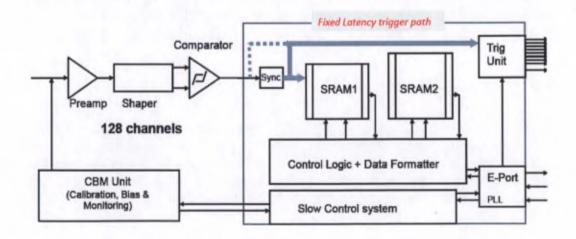

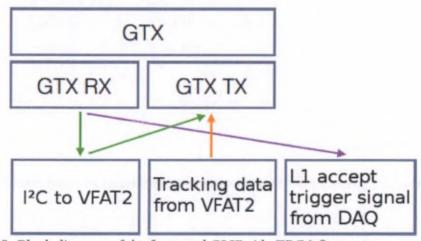

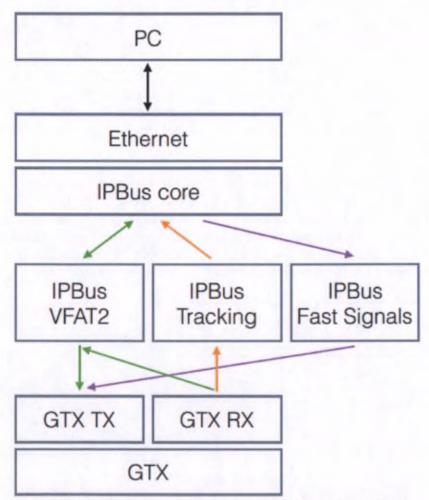

|         | .3.1 System overview                     |     |

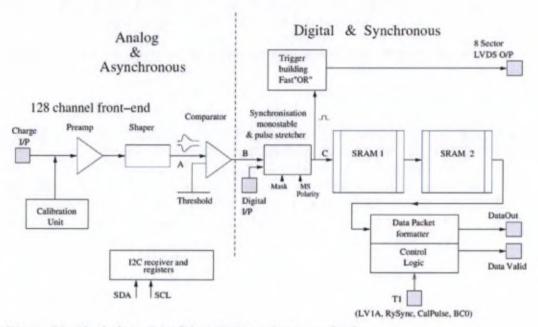

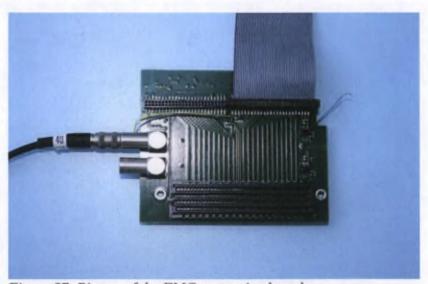

| 6.1         | .3.2 Front-end electronics               | 128 |

|-------------|------------------------------------------|-----|

| 6.1         | .3.3 Read-out electronics GLIB (µTCA)    | 130 |

|             | .3.4 DAQ software and run control        |     |

| 6.2 Res     | ults with the µTCA based read-out system | 133 |

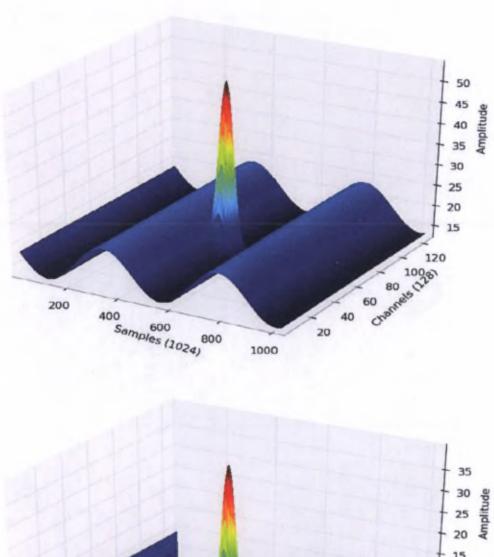

| 6.2.1       | Performance of the DAQ electronics       | 133 |

| 6.2.2       | Muon detection                           | 134 |

| 6.2.3       | Beam test results                        | 136 |

| CONCLUS     | IONS                                     | 143 |

| Bibliograph | ıy                                       | 145 |

| Table of Ac | ronyms                                   | 149 |

## INTRODUCTION

In experimental research, the most visible part of a scientific project is, by far, its scientific production. More specifically, the particularity of experimental particle physics, is the size of the projects nowadays chosen to broaden the scientific activity as much as possible in a field where the number of open questions remains predominant. In this sense, the particle physics community requires constantly bigger, more complex and higher in precision experimental facilities, making more room for non-scientific side activities, such as solving engineering challenges. This work was achieved in the context of such an experiment.

The general idea behind this work is to study a proof of concept, in the field of instrumentation and detector developments for a large scale particle physics experiment. The aim is thus to study the feasibility and evaluate the implications of installing a novel type of detector as a future upgrade of this experiment. All along this document, the emphasis is put on a technical study and technological solutions from an engineering point of view, keeping in mind the objectives and requirements imposed by the final user, namely the particle physicists. It is important to remind the reader that this study started literally from scratch, reflecting the numerous steps needed in a large design process including its successes and its dead ends.

A first chapter will describe the frame in which this work was inserted. The experiment is the Compact Muon Solenoid (CMS) collaboration, one of the experiments for which the European Organization for Nuclear Research (CERN) provides beam and experimental facilities. These two entities are described in this first chapter, after having given to the reader a short introduction on the aim and motivations of research in particle physics. During this chapter, the attention is slowly focused towards the end-cap muon spectrometer, which is the part of the CMS detector of interest in this work.

The second chapter is oriented towards the infrastructure of the CMS detector, and

more specifically, the data acquisition system. This is where the integration of a new type of detector, unforeseen in the original design of CMS, will have the biggest implications. As a matter of fact, the data acquisition system is the most constrained sub-system of the entire experimental facility. Incorporating a new sub-detector and its own data acquisition system inside this already existing infrastructure is a challenge. Understanding the architecture, the constraints and the possible extensions is the aim of this second chapter.

The studied new detector type is explained in Chapter Three. A comparison of the existing types of detectors for the detection of muons in the forward region of CMS is given first, followed by a description of the explanation of the physics goals and performance specifications. A more detailed upgrade path is given afterwards, in a chapter listing the implementation details of the proposed upgrade. A broad technical description of the components, from the front-end to the back-end parts of the data acquisition chain is given in this chapter.

The two last chapters are dedicated to the developments made to finalize the proof of concept. First, to fit into the currently planned evolution of the data acquisition system of the entire experiment, a number of developments were made according to a new chosen standard for the DAQ electronics. Moving towards this new architecture standard, called  $\mu TCA$ , a challenge for engineers in electronics. This is why a detailed study to gain experience and understand the advantages is undertaken in this work. As a conclusion to this study, the last chapter presents a mock-up system of a detector prototype and the associated DAQ chain to be implemented, built in our lab and making use of cosmic muons to generate events. Preliminary results of a very similar system tested with a muon beam at CERN are given last. Although this experimental setup is only a proof of concept, attention is given to handle the different implementation challenges as close as possible to the final system.

These very promising results and the design of the architecture are of course the result of a group work, in the name of the Brussels R&D group of the Inter-university Institute for High Energies (ULB-VUB). A number of contributions, however, are the fruit of the work of the author himself. The study of the  $\mu TCA$  standard for example, as well as all the hardware, firmware and software developments performed in this innovative standard such as described in Chapter Five, constitute the first main personal contribution. The numerical simulations of the front-end electronics signal processing functions, as described in Chapter Four are also the author's contribution, and the biggest part of the hardware and firmware developments described in Chapter Six as well. Finally, the author's knowledge in electronics, microelectronics, software developments, computing, networking and systems engineering were essential to set up an adequate engineering environment, to hold a consultative role during the planning phase of the numerous system developments on which the Brussels R&D group participated and finally, were also useful for contributing to the design of the entire GE1/1 DAQ system for the CMS muon spectrometer upgrade.

## **CHAPTER ONE**

# The LHC and CMS: The collider and the experiment

The idea that everything around us is made out of smaller elementary constituents is as old as Democritus (460 - 370 B.C.), who postulated that the universe consists of empty space and an (almost) infinite number of invisible particles which differ from each other in form, position, and arrangement. For him, all matter is made of indivisible particles, and he even gave these the name of atoms. The reason why it took more than two millennia to actually discover something that could confirm Democritus thoughts (Joseph Thompson with the discovery of the electron in 1898) is closely related to the slow evolution of technology until the 20th century. These

two thousand years saw the most brilliant minds in the history of theoretical physics. But it is only with the experimental discovery of the first elementary building bricks of matter at the beginning of last century that physicists were able to found the bases of what became a new branch of physics, namely particle physics.

This chapter is an illustration of what is mentioned above. Based on very accurate models, a set of orthogonal and well defined building bricks (later referred to as Standard Model in this chapter) and a strong sense of intuition, some new particles have been predicted before being discovered. This discovering phase is what the particle accelerators are designed for. After a short reminder of the basics needed to understand the principles behind these new discovery machines, we will focus on the technologies used to create the best experimental conditions (the LHC) and understand how we make observations (the CMS experiment) in this particular branch of physics.

## 1.1 Cultural background in particle physics

## 1.1.1 Short contextual history

Scientific discoveries are resulting from overcoming the obstacles to the broadening of our understanding of the Universe. Through the ages, the obstacles were first cultural (ancient beliefs until the Roman Empire, followed by the omnipotence of the church in Europe) until the second half of the middle ages, limits of the technological advancement (overcame with the industrial revolutions), and geopolitical in the last century. The next most probable obstacles to the coming scientific breakthroughs will be financial, as the number of funded research fields sharing the same budget exploded in the last forty years (eg. space, health, environment, social sciences). The field of particle physics is a good example, since the origins of the world and the nature of the fundamental forces were long attributed to divine instances, the experimental part of this discipline is strongly dependent of the state-of-the-art in the field of engineering and finally, the most brilliant minds in this field were brought together by a number of major events in the history of the 20th century.

After the second world war, which boosted the domination of the United States in large scale experimental nuclear physics, interest in bringing European science back to the foreground grew amongst the European scientific community. Following the post-war trend of creating international peace-keeping organizations, the idea of creating a uniting, pan-European and independent entity to promote non-military research in nuclear physics was proposed by Louis de Broglie in 1949. The main advantage of such a structure, of course, would be to rationalize the prohibitive costs of building a world-class research facility from scratch. Between 1951 and 1954 the "Conseil Européen pour la Recherche Nucléaire" (CERN), which was composed of eleven European states, settled the bases of the future entity. Finally, on the 29<sup>th</sup> of September 1954, the council was dissolved, and the European Organization of the same name was born.

CERN is located on the Swiss-French boarder close to Geneva. It enjoys a yearly budget of about one billion Swiss Francs and employs around two thousand workmen, technicians and engineers, which makes it currently the world largest laboratory in particle physics. In this sense, it is a service provider, aiming at providing facilities, raw matter (particle beams) and expertise to particle physics experiments. These experiments are usually not run by CERN itself but by worldwide scientific collaborations. They are regularly mentioned in the press for achieving major breakthroughs in the domain of particle physics of course, amongst which it would be unfair not to mention the W and Z bosons (UA1 experiment, 1983) and the now famous Higgs boson (joint ATLAS and CMS experiment [1] [2], 2012).

## 1.1.2 Introduction to particle accelerators

In experimental particle physics, we can distinguish two types of experiments

allowing the study of the existence and the properties of particles. The first type is the non-accelerator based experiment. These experiments are usually associated with astrophysical particle physics and cosmology, since the incoming bodies have been accelerated by astronomical events such as supernovae, black holes and possibly Gamma-ray bursts. The IceCube Neutrino Observatory for example, is recording the photons emitted by the interaction of neutrinos in a cubic kilometer of the Antarctic icecap under the Geographic South Pole. The second type of experiment is called accelerator-based, and is dependent on the presence of the services and facilities provided by a laboratory. The main difference between these two types of experiments is the deterministic nature of the events. In the first case, no-one knows when an interaction will happen, whereas in an accelerator based experiment, the presence of an upcoming event is known in advance. This will have consequences on the architecture of the data acquisition system. The current work was done in the context of an accelerator-based experiment, the services and experimental facilities being provided by CERN and its Large Hadron Collider (LHC).

The fundamental relation behind every particle accelerator is known as the Lorentz force law:

$$\vec{F} = q(\underbrace{\vec{E}}_{\text{electrostatic}} + \underbrace{\vec{v} \times \vec{B}}_{\text{magnetic}})$$

(1)

where  $\vec{F}$  is the force experienced by a particle holding a charge q moving at a velocity  $\vec{v}$ , inside an electrical field  $\vec{E}$  and a magnetic field  $\vec{B}$ . Accelerating and guiding the particles to reach high energy particle beams is thus a matter of cleverly combining electromagnetic fields. A good indicator of the performance of an accelerator is the event rate, in other words the amount of occurrences of the researched process per seconds (  $f_{process}$  ), given by the formula:

$$f_{process} = L \sigma_{process}$$

(2)

where  $\sigma_{process}$  the interaction cross section of the process (expressed in barns¹) and L the luminosity. The latest quantity, expressed in cm⁻²s⁻¹, is fully dependent on the configuration of the accelerator and the shape and density of the particle beam. In the case of a circular colliding storage ring such as the LHC for example, two beams circulating in opposite direction at f turns per second and containing N particles each, with a Gaussian shaped profile yielding a transverse size of  $4\pi s_x s_z$  the expression of the luminosity L is:

$$L = \frac{fN^2}{4\pi s_x s_z} \tag{3}$$

From equation (3) we can see that the luminosity, and by definition the corresponding event rate, can be increased either by squeezing the beam  $(s_x s_z)$ , increasing the revolution frequency (f), or increasing the number of particles per beam (N).

<sup>1</sup> One barn = 10-24 cm-2

A last parameter sometimes used to characterize the amount of data produced by an accelerator is the integrated luminosity over time:

$$L_{\rm int} = \int L.dt \tag{4}$$

This quantity, expressed in the inverse of a cross-section<sup>2</sup> is also used to quantify the effective operation time, in order to estimate the aging of the different components of an accelerator or experiment. In the case of the LHC for example, this measure is linked to a deposited radiation dose, which will limit the reliability of some front-end measurement electronics.

## 1.1.3 Collider experiments

Two main types of accelerator-based experiments exist. First, the fixed target experiment. When the particle masses may be neglected compared to the beam energy, the energy in the center of mass reference frame, usually noted  $\sqrt{s}$ , is given by  $\sqrt{s} = \sqrt{2E_{beam}m_tc^2}$ , where  $E_{beam}$  is the energy of the incident beam particle and  $m_t$  the mass of the target particle. It thus grows with the square root of the energy of the incoming particle. The second type is the collider experiment where much higher energies can be reached, since its energy released in the center of mass reference frame is given by the relation:

$$\sqrt{s} = 2E_{beam}$$

(5)

The challenge in this technology, however, is to make two particles coming from opposite directions at the speed of light to interact without missing each other.

As opposed to the fixed target experiment where the resulting momentum after impact is in the forward direction because of kinematics constraints, in collider experiments the products of the interaction are strongly dependent of the process underlying the interaction and therefore cylindrically symmetric detectors with sensitivity down to small angles are required. This allows the measurement of four quantities on the final states:

- Particle type

- · Spacial position and timing

- Momentum

- Energy

This cylinder is usually composed of two main regions. On one hand the barrel around the interaction point, and the end caps closing the barrel on the other hand.

By convention, the system of Cartesian coordinates (X,Y,Z) centered on the

<sup>&</sup>lt;sup>2</sup> 1/nb or nb<sup>-1</sup> - nanobarn<sup>-1</sup>; 1/pb or pb<sup>-1</sup> - picobarn<sup>-1</sup>; 1/fb or 1fb<sup>-1</sup> - femtobarn<sup>-1</sup>

interaction point is set as follows:

- X points towards the inside of the ring

- · Y points to the sky

- Z is in the same direction of the beam line.

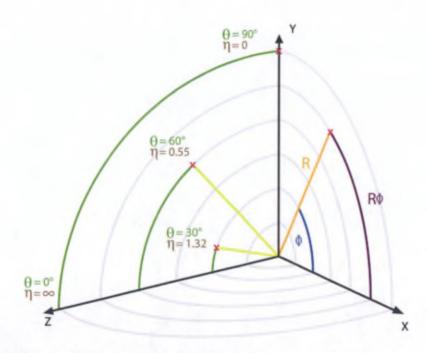

The XY plane is thus called the transverse plan. To better describe the momentum angle based physics inside a collider experiment, however, a set of polar coordinates  $(Z,\theta,\Phi)$  is more appropriate, as shown in Figure 1. Here Z is still the axis along the beam line,  $\theta$  is the polar (longitudinal) and  $\Phi$  the azimuthal (transverse) angles with Z. In addition, to equally distribute the non-symmetric nature of the final states along the  $\theta$  angle, a new Lorentz invariant called pseudo-rapidity for highly relativistic particles is defined by  $^3$ :

$$\eta = -\ln[\tan(\frac{\theta}{2})] \tag{6}$$

Below is a view of the reference frame transformation.

Figure 1: Relation between pseudo-rapidity  $\eta$  and angle  $\theta$ .

$<sup>^3</sup>$  Strictly speaking it is the rapidity, defined as  $y=\ln\sqrt{\frac{E+P_zc}{E-P_zc}}$ , which is Lorentz invariant. For highly relativistic particles,  $y\!pprox\!\eta$

## 1.2 The LHC

#### 1.2.1 Context

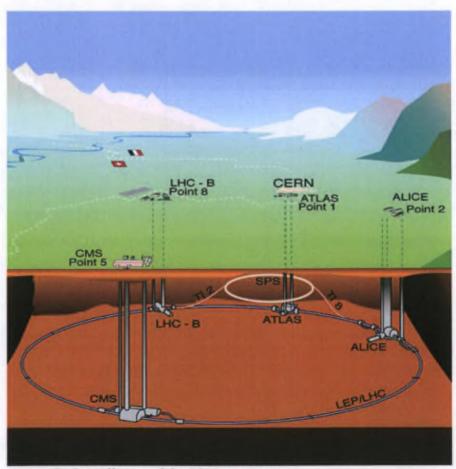

While the Large Electron-Positron (LEP) collider was still under construction at CERN in the mid-eighties, the particle physics community was already looking ahead to the next steps of the Standard Model exploration. After discussions inside the particle physics community and the letters of intent, in 1992, of the ATLAS and CMS collaborations [1] and [2], it was agreed that the next generation of particle accelerator would be a hadron collider and would be built at CERN. The choice of the location was strongly influenced by the cost savings to be made if reusing the existing infrastructure present at CERN [3], namely the LEP tunnel and the existing accelerators which we will later call the LHC injection chain. In December 1994, the CERN council gave its approval to the LHC project, and once the LEP was decommissioned and dismounted in year 2000 after 11 years of fruitful operation, the 27 km circumference tunnel, a hundred meters under the French and Swiss countryside was freed (see Figure 2) and the construction of the most complex and advanced experiment facility could start, in 2001.

Figure 2: Overall view of the LHC experiments.

The construction and commissioning of the LHC took ten years to complete. During these years many major engineering challenges were overcome, a number of civil engineering master pieces were built and a total of 6.5 billion Euro were spent [4]. A magnet quench incident in September 2008 delayed the startup by more than a year, but finally, on March the 30th, 2010, two proton beams collided at 7 TeV in the center of mass reference frame, marking the start of a new era in high energy physics.

## 1.2.2 Key parameters of the LHC

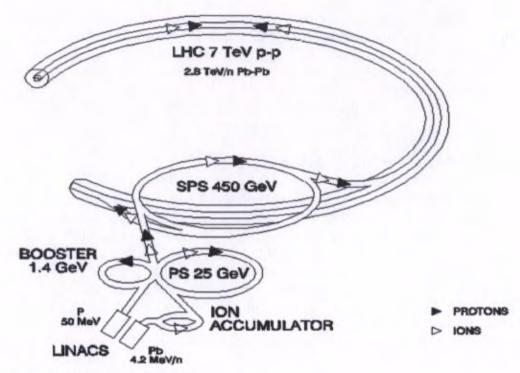

The LHC injection complex providing the beam for each run is a chain of four preexisting accelerators, as shown in Figure 3. The base unit is a bunch of about 100,000 million protons, produced by a bottle of hydrogen and a duoplasmatron. A first 50 MeV/c linear accelerator (LINAC2) followed by two synchrotrons, namely CERN's 1959 Proton Synchrotron (25 GeV/c) and the Super Proton Synchrotron (450 GeV/c) are used to inject a grand total of 2808 bunches inside each ring, according to the 25 ns scheme described in [5]. This 25 ns gap between every single bunch is an important number to keep in mind. It is the origin of the 40 MHz global LHC wide bunch crossing clock which will give the synchronization signal for all the instrumentation of the LHC and the experiments. The revolution frequency of the beam around the LHC is 11,245 turns per second. The nominal momentum after the acceleration phase inside the LHC is 7 TeV/c per beam at a luminosity of 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>.

Each run has a nominal duration of 10 hours, during which the beams must remain stable and perfectly under control for about four hundred million revolutions. This is achieved with advanced beam and instrumentation monitoring systems, combined with beam control devices such as beam scrapers and collimators. Because of the destructive amount of kinetic energy stored inside the beam, losing its control would have dramatic consequences on the infrastructure of the LHC itself. This is why an extremely reliable beam dump system was foreseen, capable of dumping the 350 MJ of each beam at once. This system is also used at the end of each run.

Figure 3: LHC injection chain [5].

## 1.2.3 Upgrade plan

Many uncertainties on the reliability of all the systems arose after the magnet quench incident of September 2008. All the magnets had been trained to reach 9 Tesla individually before installation [6]. After the incident, all the installed magnet circuits, however, were only trained to 6.5 Tesla. This limit came from a larger than expected number of quenches, and gave the limit of 3.5 TeV to the beam energy with half luminosity for a first period of operation. The decision was subsequently taken to define a first 10-year phase of operation (phase 1, 2010-2020), dedicated to carefully reach the nominal performance of the LHC, in 3 successive steps separated by 2 long shutdown (LS) periods. Beyond 2020, the phase 2 is then meant to extend the performance beyond the nominal values originally defined in the specifications, namely by doubling the instantaneous luminosity of the beams to 10<sup>35</sup> cm<sup>-2</sup>·s<sup>-1</sup>. Table 1 summarizes the different operation and maintenance periods.

The first period of phase 1, between 2010 and 2012 (7-8 TeV collision, luminosity of 0.5 \* 10<sup>34</sup> cm<sup>-2</sup>·s<sup>-1</sup>) was meant to produce enough collisions, in order to perform a thorough Higg's search in the missing mass range between CERN's LEP experiment (114 GeV/c<sup>2</sup>) and Fermilab's Tevatron accelerator (600 GeV/c<sup>2</sup>). This was a success, since 30 fb<sup>-1</sup> of integrated luminosity [7] were produced in the LHC and allowed the discovery of the famous missing particle in the Standard Model. After a first long shutdown (LS1) of two years, needed mainly to rework the interconnections of all the bending magnets, the planned performance of 14 TeV collisions at the center of mass

reference frame and a nominal luminosity of 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> will be achieved, at the beginning of 2015. Two years of operation at this level are foreseen, before a new long shutdown where some LHC systems will be modified for operation with double of nominal luminosity. These two last years of phase 1 operation are of particular interest in this work, since this is the target period for the systems design described in the next chapters.

After 2021, a phase-2 is scheduled with a luminosity increase of a factor of ten, to reach an ambitious 10<sup>35</sup> cm<sup>-2</sup>·s<sup>-1</sup>. Since only the beam current is increasing, the major challenges are not on the LHC side, but on the experiments. In most of the maintenance periods of phase 1, the detectors undergo small improvements, but no major structural changes. For phase 2, however, the entire detectors and associated data acquisition systems need to be upgraded, to be able to handle a factor ten increase of events per bunch crossings. On the facilities side, provided by CERN, this upgrade will see the commissioning of a new injection complex, replacing the aging PS and LINAC, and upgrading significantly the SPS.

| Period        | Energy                | Luminosity                                             |

|---------------|-----------------------|--------------------------------------------------------|

| 2010-2012     | 7-8 TeV               | 0.5 * 10 <sup>34</sup> cm <sup>-2</sup> s              |

|               | Long Shutdown 1 (LS1) |                                                        |

| 2015-2017     | 13-14 TeV             | 10 <sup>34</sup> cm <sup>-2</sup> ·s <sup>-1</sup>     |

|               | Long Shutdown 2 (LS2) |                                                        |

| 2019-2021     | 14 Tev                | 2 * 10 <sup>34</sup> cm <sup>-2</sup> ·s <sup>-1</sup> |

|               | Long Shutdown 3 (LS3) |                                                        |

| 2022-2030 (?) | 14 TeV                | 10 <sup>35</sup> cm <sup>-2</sup> ·s <sup>-1</sup>     |

Table 1: Summary of the foreseen energy and luminosity upgrades of the LHC [3].

## 1.3 The Compact Muon Solenoid (CMS) detector

### 1.3.1 Facts and figures

Four large experiments have been built along the LHC, one around each of the interaction points. The Compact Muon Solenoid (CMS) is one of them. It is with ATLAS, one of the two general purpose detectors. Physically, it is 21 meters long, 15 meters in diameter, is built of about 100 million individual pieces and weighs 21,000 tons. Furthermore, the CMS collaboration is made of over 4,300 active members of 182 institutes from 42 different countries around the world<sup>4</sup>.

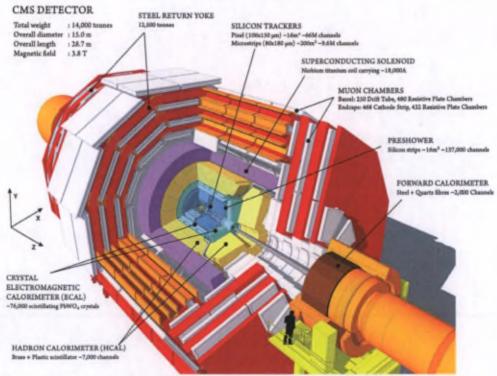

As most of the collider experiments, CMS is built of the usual main components, as shown in Figure 4. In the barrel region of CMS, a silicon tracker is the first layer around the interaction point. It determines precisely the momentum and scattering angle of the charged particles produced in the collisions. Next, electromagnetic and hadron calorimeters define the type of the scattered particles and their energy. All this is possible with the help of the magnetic field produced by a solenoid in the next layer. Finally, the outside of the barrel and both end caps are built of muon chambers. The latest are part of the subject in the current work.

Figure 4: Representation of the different parts of the CMS detector.

<sup>4</sup> As of this writing

#### 1.3.2 Barrel

This description of the CMS detector starts with the barrel, from the origin at the interaction point (IP) to the outer layers.

#### 1.3.2.1 Silicon tracker

The very first layer around the beam line is the silicon tracker. Its role is to track the momenta and the scattering angles of the charged particles leaving the interaction point. Two types of semiconductor detectors are used for this purpose, the pixel and the strip detectors. The advantage of these technologies are multiple. First, the spatial resolution which is of the order of 20 microns for the pixel detectors in CMS. This allows very accurate tracking capabilities and a momentum reconstruction resolution of 1% close to the IP. The second main advantage of silicon detectors is the excellent time resolution, since the recovery time after an event is smaller than the bunch crossing frequency. The trade off for this type of detector is the price. They are usually installed where it is strictly necessary, usually at the very center of the detector.

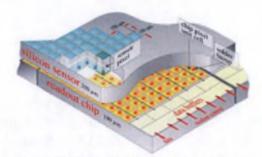

A pixel detector is made of a PN junction based detection layer, stacked on top of a readout layer. Reverse biasing the PN junction creates an electric field. The interactions produced by a charged particle traveling through the dense silicon create electron-hole pairs, each drifting to the electrode, where the readout front-end array converts the produced current into a signal.

Figure 5: View of a CMS silicon pixel detector stack.

Figure 5 shows the layout of a small part of the CMS silicon pixel detector. The size of each detection layer area is  $150~\mu m^2$ , and each of this pixel requires its associated readout front-end. As a result, this exceptional density is at the cost of a complex individual wiring scheme. This is usually the limiting factor to the pixel density of a tracker.

Three layers of these pixel detectors are placed around the interaction point to allow an accurate track reconstruction. The next layer of the tracker are made of silicon strip detectors. The detection principle is the same, but the shape of the detection area becomes a strip. This reduces the amount of expensive pixels as the surface of the cylinder increases, but enables detection only in one single dimension. The spatial

resolution is decreasing accordingly to a minimum of 50 microns on the outer layer.

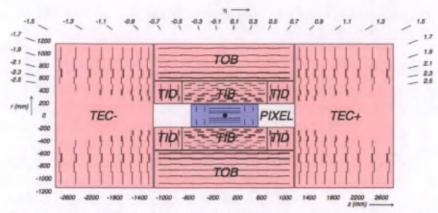

Figure 6: View of the tracker layout. In blue the pixel detectors, in red the strip detector.

Figure 6 shows the overall geometry of the CMS silicon tracker. The pixel detector is made of three layers in the tracker barrel and two disks in the tracker end cap. The silicon strip detector is made of ten layers in the tracker barrel (TIB + TOB), three layers in the disks (TID) and nine disks in the tracker end cap (TEC). The trajectory of the charged particles is influenced by the strong magnetic field generated in the solenoid. The bending radius, in meters, is given by the relation:

$$R = \frac{P_T}{0.3B} \tag{7}$$

where  $P_T$  is the transverse momentum of the scattered particle in GeV/c, and B the strength of the magnetic field in Tesla. Measuring the bending direction of the scattered particle gives us its charge and the bending radius reveals the momentum. This, of course, requires an accurate correlation search between the different layers of the silicon tracker.

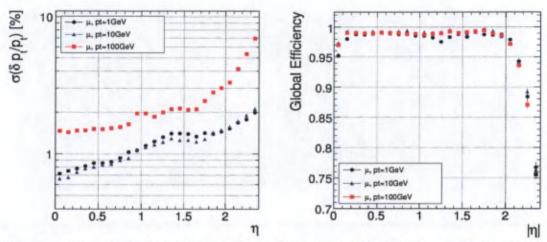

The performance of the silicon tracker for muons in the 1, 10 and 100 GeV/c range, is given in Figure 7.

Figure 7: Transverse momentum resolution (left) and tracker efficiency (right) with respect to the pseudo-rapidity.

As expected from the layout given in Figure 6, the efficiency and the resolution are strongly dependent of the pseudo-rapidity, with a remarkable level of precision for  $|\eta| < 1.5$ , and a rising imprecision beyond this value. This is due mainly because of the higher material density in this region, producing more scatterings, combined with a decreasing strip density.

#### 1.3.2.2 Electromagnetic Calorimeter (ECAL)

Immediately next to the silicon tracker is the electromagnetic calorimeter. The role of a calorimeter is to absorb and measure the energy of electrons, positrons and photons. It makes use of the cascades of secondary particles that incident particles produce via repeated bremsstrahlung and pair production processes inside the material of the calorimeter.

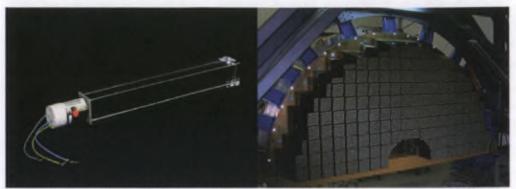

In CMS, for instance, the ECAL is built out of 75,000 PbWO<sub>4</sub> crystal scintillators, each coupled to a photomultiplier tube to amplify and collect the emitted photons. In this type of crystal, the radiation length<sup>5</sup> of an electron is in the order of a centimeter and the Molière radius<sup>6</sup> is about 2.2cm [8] Accordingly, each crystal has an area of 2.2cm<sup>2</sup> for a length of 23cm (see Figure 8).

$<sup>^5</sup>$  The radiation length (  $\lambda_R$  ) is the distance traveled by an electron before interacting

<sup>&</sup>lt;sup>6</sup> The Molière radius approximates the size of a contained electromagnetic shower

Figure 8: One CMS ECAL crystal (left). CMS ECAL crystals setup in one half of an end cap (right) [9].

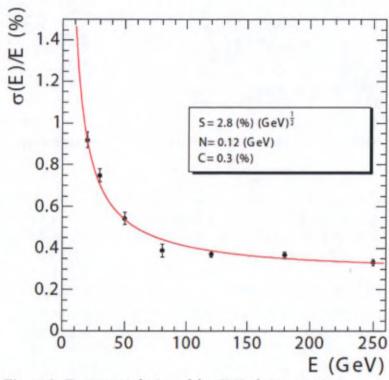

The energy resolution of the electromagnetic calorimeter is given by the relation:

$$\left(\frac{\rho_E}{E}\right)^2 = \left(\frac{a}{\sqrt{E}}\right)^2 + (b)^2 + \left(\frac{c}{E}\right)^2 \tag{8}$$

where a is the stochastic term representing the number of particles produced in the cascade, b is a calibration constant and depends on the quality of the crystal, and c is a noise factor induced by the electronics. As we can see, the behavior of a calorimeter differs significantly with respect to a silicon tracker in the sense that the resolution improves with the energy. One of the technical challenges for this system is the evolution of the b factor over time, these crystals tending to become opaque with the ambient radiation in the center of the detector. A systematic recalibration of this sub detector will thus be performed during the operation time of CMS. The energy resolution for the CMS ECAL at commissioning time was given by the factors:

$$\left(\frac{\rho_E}{E}\right)^2 = \left(\frac{2.85\%}{\sqrt{E}}\right)^2 + (0.3\%)^2 + \left(\frac{12\%}{E}\right)^2$$

(9)

which is illustrated below:

Figure 9: Energy resolution of the CMS electromagnetic calorimeter [9].

### 1.3.2.3 Hadron Calorimeter (HCAL)

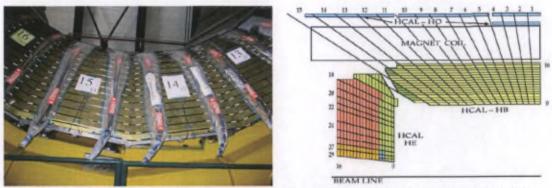

Hadrons are another byproduct of proton-proton interactions. A hadron calorimeter relies on the strong interaction force between the incoming hadrons and a very dense medium, called an absorber, to produce cascades. Since the energy range of the interacting hadrons is broad, the radiation length is significantly longer than in the case of electromagnetic interactions. The HCAL thus requires a much larger amount of absorber material, such as steel, copper and gold. In this sense, the hadron calorimeter at CMS is built of an alternation of 16 layers of absorber and plastic scintillators in between, for a total thickness of about a meter in both the barrel and the end caps as seen in Figure 10. This corresponds to more than 5 times the nuclear interaction length?

$<sup>^7</sup>$  Nuclear interaction length  $\lambda_a$  is the mean distance traveled by a hadron before undergoing an inelastic nuclear interaction with the medium

Figure 10: View of the hadron calorimeter (left) and detail of the segmentation (right).

Here also, the effects of the ambient radiation will impair the overall performance of the sub detector. A complex network of optical fibers is laid out along the scintillators to inject calibration pulses. This in order to measure and adjust the b parameter in equation (8) during off-line analyses.

#### 1.3.2.4 Superconducting solenoid

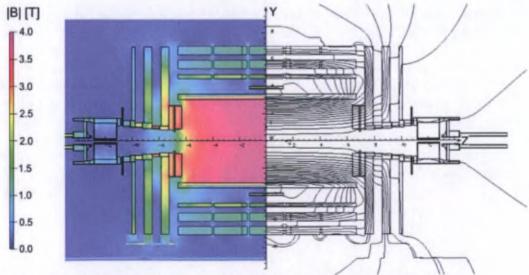

The strong magnetic field needed to measure the transverse momentum of the charged scattered particles is created by a 12.5 meter long solenoid coil around the hadron calorimeter. The advantage of a solenoid coil is the uniformity of its created field in the center, as shown in Figure 11. But creating a 3.8 T capable magnet of this scale is, however, a challenge. To achieve this, the entire spool is enclosed in a cryostat container and cooled down to 4.5 °K to reach below the superconducting temperature threshold of the *niobium-titanium* windings. The power supply required to energize the magnet is rated at a power of 520 kW.

Figure 11: Simulation of the magnetic field produced by the solenoid[10].

The term "compact" in the acronym of CMS comes from the design of this magnet. Measuring the transverse momentum of a charged particle always requires a uniform magnetic field. At high energies, however, the size of detectors grow, making it expensive and technically difficult to use solenoids. To overcome this problem, the ATLAS collaboration built a toroidal magnetic field around the outermost sub detectors of the experiment. CMS, on the other hand, chose to deeply build-in the magnet inside the barrel in order to limit its size, hence the "compact". This has also as consequence to increase the spatial resolution of the inner sub detectors. The trade-off of this design is that the remaining, and usually voluminous muon chambers, are on the outside of the solenoid. In the case of CMS, this external sub detector takes advantage of the returning (opposite direction) magnetic field lines which are canalized by a steel yoke around the solenoid. Most of the impressive weight of CMS come from this yoke of 10,000 tons on its own. Figure 12 shows the steel yoke components of CMS.

Figure 12: View of the yoke elements around the solenoid [9].

#### 1.3.2.5 Muon chambers

The dense materials present in the hadron calorimeter and the solenoid were chosen with an absorption interaction length<sup>8</sup> of about 17 cm, which is short enough to absorb the entire hadron energy. In addition, since the energy loss by bremsstrahlung depends on the particle mass as shown in equation:

<sup>8</sup> The nuclear absorption length is the scattering distance of a hadron in a medium

$$\left\langle \frac{-dE}{dx} \right\rangle \propto \frac{E}{m^2}$$

(10)

only muons and weakly interacting particles such as neutrinos are still present beyond the coil. This is thus where the muon chambers are located, assembled inside the layers of the magnet yoke, where an opposing magnetic field exists.

Figure 13: View of the barrel muon stations.

The muon system is the biggest sub detector in terms of surface, with a total covered area of 25.000 m<sup>2</sup> of detector planes. To make the design cost effective and robust, the choice was made to install gas detectors in the barrel region. Since this document is mainly focusing on the muon system, a complete description of the current state-of-the-art muon chambers will be given in Chapter Three.

## 1.3.3 End caps

The second part of the detector is composed by the two end caps, which are essentially built of muon chambers.

#### 1.3.3.1 Muon chambers

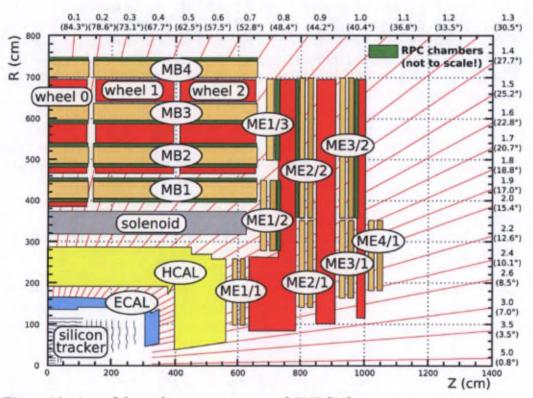

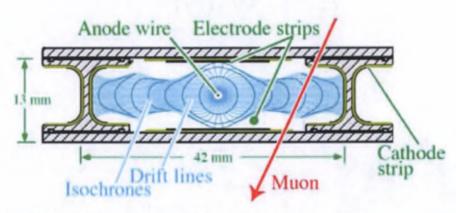

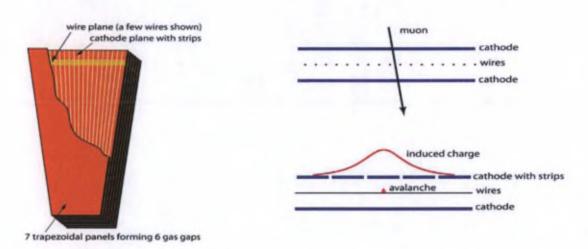

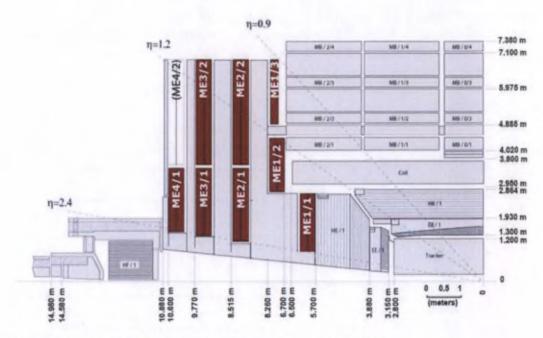

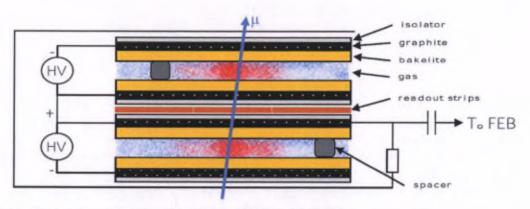

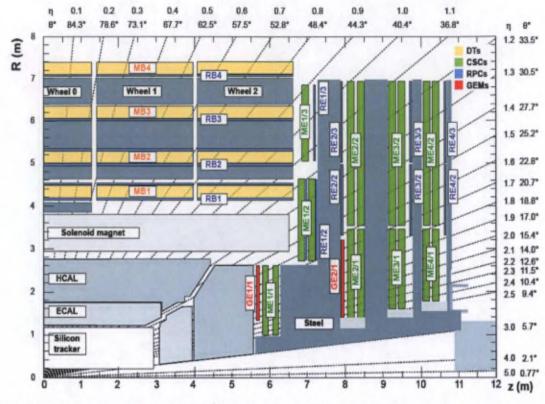

The end cap muon system is the subject of this work. The barrel muon chambers cover a pseudo-rapidity of  $|\eta| < 1.2$ . Beyond this angle, the muon flux is caught by the end cap muon system. Two technologies currently coexist in this system, namely Cathode Strip Chambers (CSC) and Resistive Plate Chambers (RPC). Both technologies are described in Chapter Three of this document.

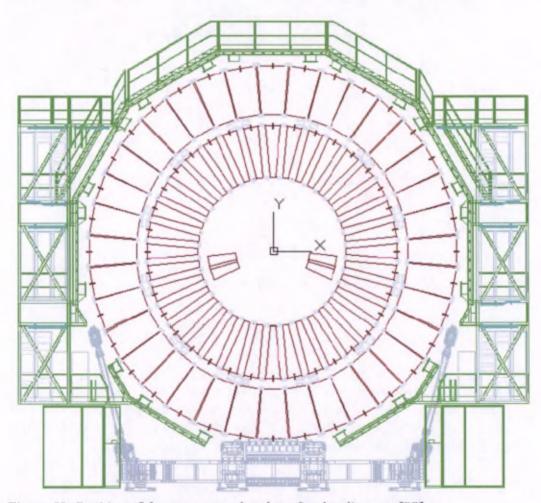

The layout consists in consecutive layers along the Z direction, in order to allow precise momentum measurements by finding coincidences between hits on the trajectory of a muon. For redundancy reasons, the CSC and RPC chambers are both installed in parallel in the  $0.9 < |\eta| < 1.6$  region. Initially it was planned to have RPC detectors up to  $|\eta| < 2.4$ . However, for economic reasons and because it was expected that the muon setup would perform well without RPC's in the range  $1.5 < |\eta| < 2.4$  during the first years of LHC running when the luminosity would be much lower than the nominal value, it has been decided to stage the installation of RPC's in the highest  $\eta$  region. The space for these chambers was nevertheless foreseen in the end caps, and left empty for the initial startup up in 2010. These empty spots are of importance in this work as we will see in Chapter 3. Below is a view of the end caps. MB stands for the muon chambers in the barrel region and ME locates the muon system locations in the end caps.

Figure 14: view of the end cap muon system of CMS [11].

#### 1.3.3.2 Forward Calorimeter

About eleven meters away from the interaction point, measuring between a pseudorapidity of 3.0 and 5.0, is the forward calorimeter. Its focus is on hadron products of the collisions, namely in the form of high density jets. The cascades are created by heavy steel blocks, with embedded fibers to detect Cherenkov light. The main research topic of this sub detector was Higgs productions at high mass. Since this channel is now excluded by the discovery of 2012, the main goal of this calorimeter is now to improve the accuracy of the missing transverse energy measurement.

## 1.3.4 Upgrades

In the coming years, following the LHC upgrade plans, CMS will improve some of its sub detectors in order to adapt the experiment to the foreseen luminosity upgrade, complete several missing functions on the initially installed setup, and to refocus on some aspects of the physics program. For instance, now that a low energy (125 GeV/c²) Higgs scenario has been validated, the upgrades of the LHC and the detectors will allow to focusing on the in-depth study of this particle's properties.

CMS was not built to operate at, nor to withstand the effects of, a luminosity upgrade such as planned at the end of LHC Phase 1 (2019-2020) and phase 2 (beyond 2021), see Table 1. The silicon tracker needs to increase its resolution to avoid significant signal losses at higher interaction densities. In addition, for phase 2, the tracker will have to participate in the trigger decision, which is not the case for the current tracker (see section 2.2.1). This task involves a significant R&D program and won't be ready before the last long shutdown of phase 1 in 2017-2019. For this luminosity upgrade, the entire trigger system needs to be redesigned in order to handle the foreseen average of 20 collisions per bunch crossing and the associated amount of generated events pile up. But one major upgrade is of importance in this work, namely on the end cap muon system.

As was explained in the previous section, some spaces originally foreseen for RPC detectors were left empty at high pseudo-rapidity in the end cap. A particularity of the RPC technology is the degradation of the efficiency as the rate increase. This will become a limitation for the luminosity upgrade of the LHC and makes now the RPC a non-viable solution to fill the spaces initially foreseen for them. This work is part of a feasibility study on the implementation of another technology to replace the initially foreseen RPC chambers at  $|\eta| > 1.6$  in the end caps. This novel technology is extensively described in Chapter 3.

A second major topic in the CMS upgrade plans in relation with this work is the improvement of the data acquisition system (DAQ) electronics. The current infrastructure standards used to host the read out electronics is of an older design and will certainly not be able to withstand the dramatic throughput increase associated with the high luminosity upgrades. Another, more modern, infrastructure standard was chosen inside CMS, and the design of the new muon systems based on this new standard will be the topic of Chapter Four.

## 1.4 Conclusion

We have seen in this chapter that experimental particle physics is a field where large collaborations building over-sized detectors are often required to make discoveries nowadays. CERN is one of the few laboratories hosting these experiments in the world, and CMS is a good example of their size and growing complexity. Throughout this chapter, we learned about different sub-detectors of CMS, to get the big picture of all the sub-components which may be of importance during this study. Narrowing down to the basic principles and key parameters of each of this detector layer allowed us to grasp the challenges of physics processes measurements in the context of collider experiments.

Particle interactions in these experiments are very complex events to analyze, due to the high number of different elementary elements released, and the large energy range window to focus on, in order to see these elements. Many detection layers are usually assembled around the interaction point to identify every constituents. To form a complete picture of an event, all the data from each of these sub-detectors are assembled into a main, detector-wide trigger and data acquisition system. This is the topic of the next chapter, specifically for the CMS experiment.

## **CHAPTER TWO**

# The CMS trigger and data acquisition system

As we have seen in the previous chapter, CMS is made out of numerous sub detectors of different technologies, representing millions of heterogeneous signal channels. All these technologies have their specificities, calibration parameters and timing constraints. Nevertheless, the signal of each individual channel has to be conditioned, read out, centralized and transmitted to an event builder which will condense the signals to form an event dataset ready for off-line analysis. This entire chain is called the Data Acquisition system, further referred to as DAQ. In large scale experiments such as in the field of collider physics, the DAQ system requires the use of a broad range of

technologies, amongst which electronics, computing and networking are the backbone. Although this work is focusing on the electronics developments of the muon system DAQ for the next upgrade of CMS, a broad understanding of the CMS wide DAQ is needed and will be explained in this chapter.

A first section will give a quick explanation of the different concepts and definitions in the field of DAQ systems, and in particular the strengths and important points of the trigger system. In CMS, 75 million channels are producing data at every bunch crossing. Due to technical limitations on the bandwidth and processing power of the data storage stages, a number of filtering layers have to be applied to this massive data stream without loosing any information on already low cross-section processes. This is the role of the trigger system. A second section will thus give an overview of the trigger system of CMS, followed by a broader view on the architecture of the data path in this detector. A last section will focus on the hardware implementation of these systems, with an emphasis on a new standard chosen for the coming upgrades.

## 2.1 Basic DAQ design features

In the case of collider experiments, the event rate is always given by the bunch crossing frequency, for example 40 MHz in the case of the LHC experiments. This rate is usually high and reading out every sensor channel at this rate is beyond the technical and financially affordable capabilities of today's networking and storage technologies. To limit the amount of data processed, only the hit channels are recorded. Given the fact that the multiplicity<sup>9</sup> depends on the number of individual interactions at each bunch crossing, the initial scaling of the DAQ architecture is function of the luminosity of the accelerator, which is known during the design phase of a general purpose experiment such as CMS. Concerning the individual sub detector systems, the data volume is function of the event rate such as defined in Chapter One, the area covered by the detector and the granularity of the readout electronics.

Besides transmitting only the hit channels data from the front-end electronics, some advanced filtering is usually performed in order to limit the required bandwidth of the DAQ infrastructure. Paradoxically, two parallel data paths from the front-end to the central DAQ system usually coexist to achieve this filtering. First, a fixed and low latency trigger data path is providing an interruption-type signal to the DAQ instrumentation when a channel shows a hit signal. This allows a first level of fast decision filtering, based on coincidence patterns in regions of interest. Based on this trigger data, if the fast decision algorithm running inside the DAQ system validates the existence of a detector-wide event, the channel data, also called full granularity or tracking data, is read out over the second unconstrained latency channel. Inside the front-end electronics, the event data is usually stored in a circular buffer memory area, and tagged by bunch crossing number to allow its effective retrieval by the DAQ when requested.

The processing power as well as the communication channels bandwidth, both giving the latency constraints of this first level triggering system, are critical. This is explained by the size of the detector. In a fairly large detector, such as modern collider experiments, the flight time of a muon to reach the forward detection region can be longer than the bunch crossing period. This results in a first level of events pileup in the CMS detector. In addition, the trigger decision time which depends on the length of the trigger data path, is typically much longer than the time between two consecutive bunch crossings. The circular buffer memory used to store the successive events inside the front-end chips is usually limited in size. As a result, it is important to define a latency budget for the trigger path, counted in number of bunch crossings and which should never exceed the storage depth of the buffers inside the front-end electronics. This latency budgeting is one of the most important points when designing a DAQ system, and will come back later in this work.

Beyond the experiment specific trigger system, the rest of the data acquisition system for processing events data is less demanding in terms of bandwidth and latency. The event builders used to assemble the event data of all the relevant parts of the detector

<sup>&</sup>lt;sup>9</sup> The multiplicity is the number of simultaneously hit channels per bunch crossing

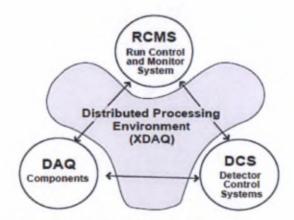

into one coherent dataset, for example, are software engines relying on general purpose IT infrastructure. This enables a high level of scalability and tends to ease the development and integration of auxiliaries such as experiment control interfaces for operators and automation or supervision functions for slow control and monitoring. Although these functions are not visible from a physics point of view, they are considered as being part of the DAQ system, since most of modern physics experiments contain large pieces of industrial infrastructure, such as water cooling, gas distribution and high voltage power supplies.

## 2.2 Overview of the CMS trigger system

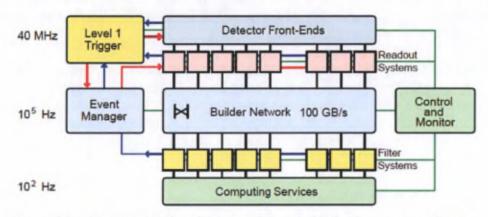

At a collision rate of 40 MHz and taking into account every readout channel, the aggregated data rate produced by CMS is about 100 Gbit/s [12], which is far more than any storage technology can handle so far. Building an efficient trigger system architecture to significantly reduce this data stream without loosing events was the complex task of the trigger design group, especially given the performance specifications. For example, where the ATLAS detector has three levels of triggering to reduce the data volume for each event, the CMS detector has only two:

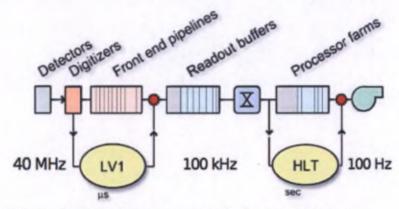

Figure 15: CMS trigger system block diagram with the data rates between each level

The main advantage of having fewer trigger levels is the direct availability of much more unfiltered data in the case an event has been accepted. The event reconstruction is thus more accurate and the precision higher. The required processing power to achieve such a flat trigger function in a delay of no more than several bunch crossings, on the other hand, is much more of a challenge. This section will first focus on the two layers of the trigger system of CMS, and subsequently on the muon system trigger mechanism and its hardware implementation.

## 2.2.1 Level-1 trigger (LV1)

For each bunch crossing, the sensors of the entire detector are read out and recorded locally in memory buffers inside the front-end electronics. Inside each of this piece of hardware, a local threshold-based decision trigger sends out a signal to a local sector trigger concentrator if the collision produced a signal with a sufficient magnitude to possibly be a valid hit. Several layers of concentrators, aiming at recognizing local patterns and coincidences, are stacked on top of each other to reach the uppermost global trigger system. This is depicted in Figure 16. If a valid trigger pattern is found, a Level-1 accept signal (produced by the Global Trigger Processor) is sent back to the entire detector, containing the bunch crossing number and a command to retrieve the corresponding data. Since most of the front-end electronics is highly optimized for

fast processing as well as for radiation tolerance, the amount of memory in the event data buffers is limited. On the muon system read-out chips, for example, a maximum of 128 events can be stored in the circular buffer before the memory location is overwritten. At a 25 ns bunch crossing period, this gives a total latency of 3.2 μs, during which the entire triggering chain is solicited, up and downwards.

Figure 16: CMS trigger data decision flow [12]

It is needless to say that each individual step in the decision flow should not exceed one or two bunch crossings, in order not to add up to the latency of every communication channel. Packeting/unpacking, modulating/demodulation and propagating an optical signal over a fiber, for example, can be done in a fixed-latency manner. However, it can take several tens of bunch crossing slots over a long distance link, especially between the front-end electronics and the global trigger systems located in the service caverns of CMS. To minimize this layered processing time, the algorithms are parallelized as much as possible. This is possible with the help of modern high density programmable logic, such as Field Programmable Gate Arrays (FPGA).

The advantages of this technology are multiple. Close to the detection areas, the radiation levels usually require the use of dedicated Application Specific Integrated Circuits (ASIC), of which we will see an example later with the VFAT2. But further away from these active zones, concentrating the numerous links not only requires high channel density electronics, but also scalability to control the development costs and adaptability. This last point was the key point promoting the use of FPGA, since the pattern recognition and coincidence search algorithms were likely to evolve with the recalibration and the better knowledge of the detector. The lucky consequence of this is that today, these trigger algorithms which are likely to evolve and be adapted for the coming updates, will require minimal hardware intervention, since a remote upgrade of the firmware can take care of this.

## 2.2.2 High Level Trigger (HLT)

The drastic data reduction operation achieved by the first level of the CMS trigger system allows a more flexible second layer of filtering at an incoming rate of 100 kHz. Processing events at this rate is possible with modern data center technologies, allowing a streamed processing time per event of the order of a second. This second level is called the High Level Trigger and is performed by software algorithms running on a computer farm of about a thousand processing nodes. The resulting data, when accepted by the triggering software, is finally stored in a distributed storage vault for later off-line scientific analysis at a rate of hundred events per second. Something to keep in mind is that the reduced dataset collected for each event is about 1.5 Mbyte, resulting in several hundreds of megabytes per second of data to be stored during each LHC run.

The technology used for this sub-system is commercial off-the-shelf IT infrastructure. Only the software architecture is designed and built in-house. An extensive description of this architecture and implementation is given in [13], but is beyond the scope of this work.

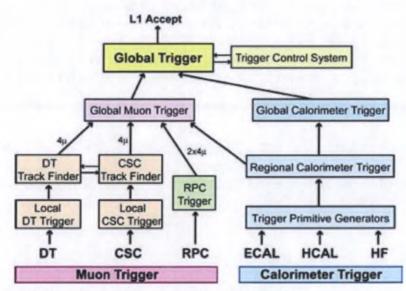

## 2.2.3 Muon system L1 trigger

As we can see on Figure 16, the muon system local triggering logic is a big part of the entire L1 trigger system of CMS. The main reason for this is the diversity of sources and resolutions in the muon system, as well as the complex timing scheme caused by the size of this sub-detector. The good spatial resolution of the drift tubes (DT) and the cathode strip chamber (CSC) for example allow these to be used as transverse momentum trigger in the magnetic field of the barrel area. Each of these technologies have thus their dedicated but similar local and regional threshold trigger and track finder electronics. The resistive plate chambers (RPC), on the other hand, are not dependent of any form of drift, and as a consequence, have a much better timing resolution (~ 1 ns). This will allow very accurate bunch crossing (BX) identification, requiring its dedicated electronics.

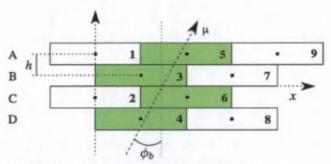

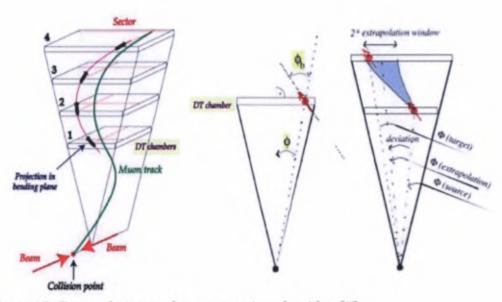

In the barrel region, the DT local trigger is defined by a coincidence detection on the cathodes of four consecutive modules. In addition to finding the position of the muon track in the DT modules, computing the drift time between layer pairs makes it possible to find the azimuthal angle  $\Phi$  of the muon, as depicted in Figure 17. The disposition of the DT modules is done in such a manner that coincidences of drift times are comparable and easy to pair. The number of pairs will define the quality of the track. This simple disambiguation mechanism is fast and efficient, and provides a good quality local trigger to the track finder.

Figure 17: Muon track position and angle measurement in DT [9]

Similarly, the CSC local trigger provides an accurate  $\,^{\eta}\,$  measurement in the end cap region by finding coincidences amongst hit cathode strips. The only difference being that, to decrease the processing time, strips are grouped with a fast OR logic operation by clusters of 5 to 16 strips inside the electronics. On top of the local track reconstruction, the track finder algorithms are identical for the DT and CSC systems. A powerful track extrapolation method using the incoming angle  $\,^{\phi}\,$  is used to send the most plausible tracks to the Global Muon Trigger (GMT). This method is based on lookup tables (LUT) where the simulated curvature parameters of the best fitting tracks are stored are retrieved. The advantage of LUT is the very fast access time, and thus the low latency cost on the entire L1 trigger system.

Figure 18: Extrapolating track reconstruction algorithm [9]

However, due to the presence of noise, the hit position uncertainty in each muon detection layer and the large size of the muon spectrometer, the track finder algorithm

often computes more than one muon candidate. A voting scheme based on the best match between measurements and extrapolated tracks retains a maximum of four candidates and send these to the GMT. Given the bending and the position inside the detector, the transverse momentum is estimated and provides an extra decision variable for the global L1-trigger system.

Concerning the RPC, several layers of these chambers are spread all over the detector to provide a very accurate trigger window to the rest of the muon system. Unlike the DT and the CSC, no local coincidence is processed for the RPC. To find the transverse momentum of an incident muon, a region-wide RPC trigger system concentrates the strip signals. A pattern comparison algorithm (PAC) is applied, based on lookup tables produced by simulations performed beforehand. Here again, a number of possible tracks are resulting after the calculation. The two most suitable tracks from the barrel are added to the two best tracks in the end caps and send to the GMT.

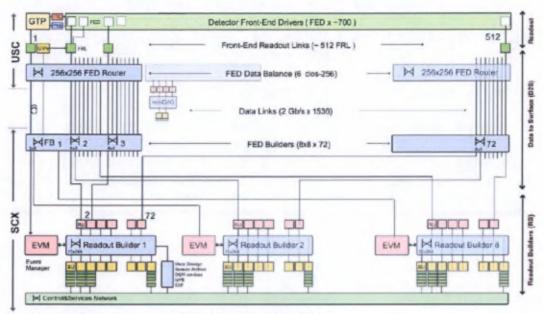

## 2.3 The CMS Data Acquisition System architecture

In addition to the already complex dual stage trigger system, the rest of the DAQ is also impressive. The data readout stage, for example, is meant to retrieve the tracking data from millions of channels, sectored in more than 650 sources at a time, once a L1-accept trigger is issued by the Global Trigger Processor. This operation is performed asynchronously, to make the best usage of the front-end electronics processing resources and communication channels. In the case of CMS, all the retrieved data is processed in an event builder, composed of a farm of standard personal computers. Once the event datasets are built, an event filter coupled to the HLT is applying a last level of data reduction, and dispatches the datasets to the different storage vaults with an acceptable speed for today's storage technology. Finally, a parallel monitoring and control system is providing an interface to the detector operators of the entire DAQ process.

Figure 19: The CMS DAQ architecture [9] with the data rates at each stage

### 2.3.1 Event readout interface

Each sub-detector is assigned a number of Front-end Readout Links (FRL) to the central DAQ system according to its granularity. These FRL are optical link inputs with a defined communication protocol and data format. The readout and the concatenation of the individual sensor channels is left to the responsibility of sub-detector collaboration. The FRL electronics is composed of a sub-detector specific Front-End Driver (FED) board, which is pushing the region data towards the central DAQ system over the FRL once an L1-trigger is issued. Below is a table summarizing the number of FED allocated to each sub-detector.

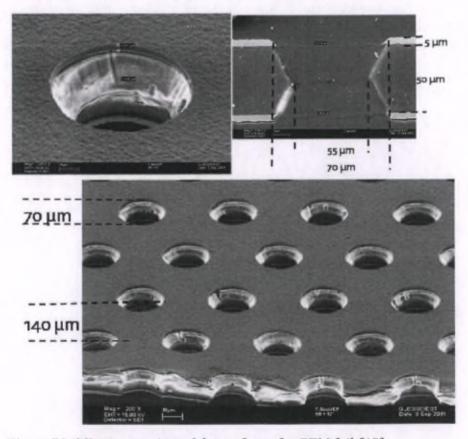

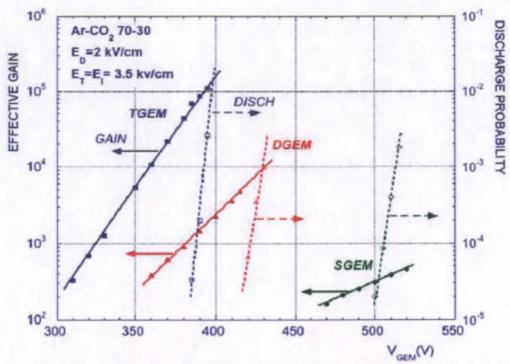

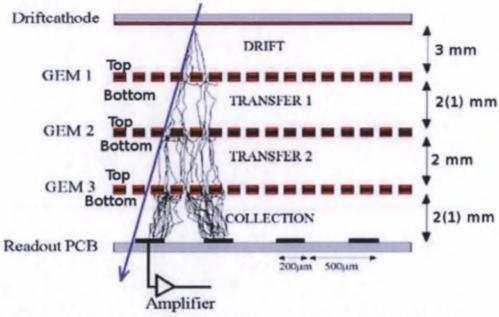

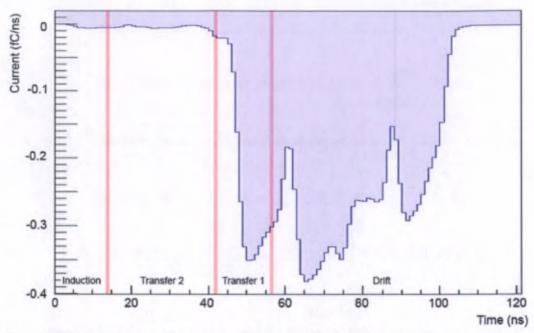

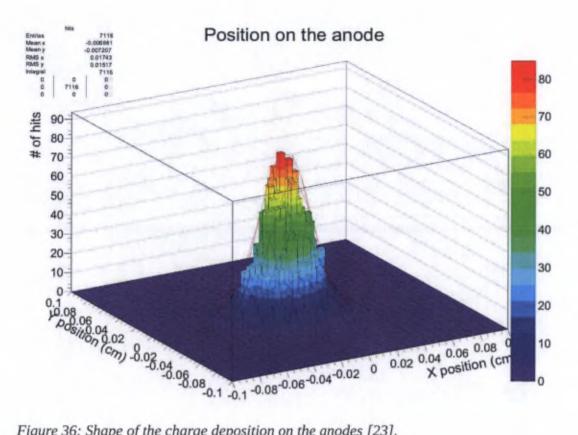

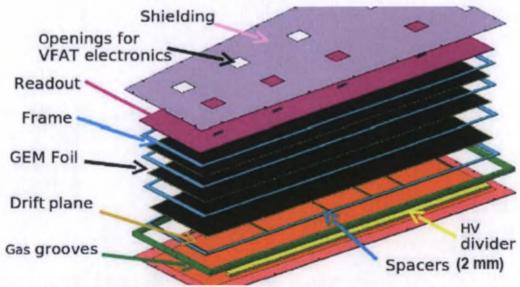

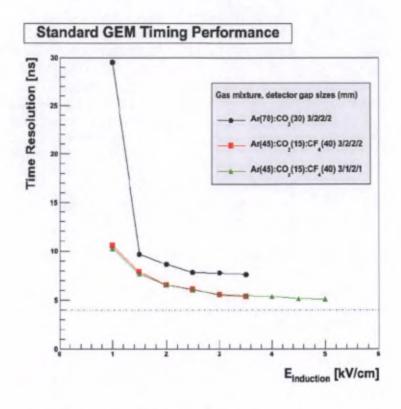

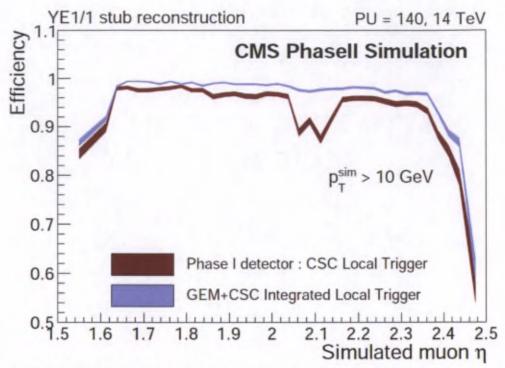

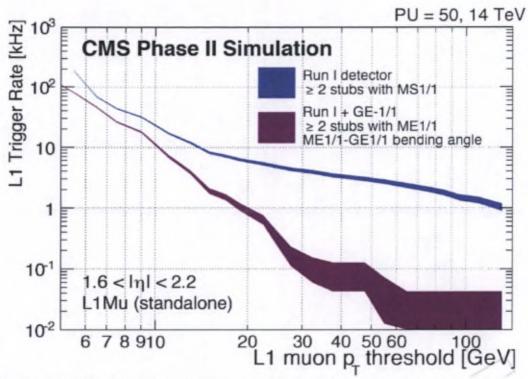

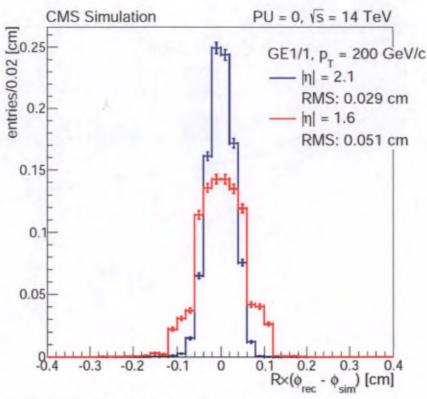

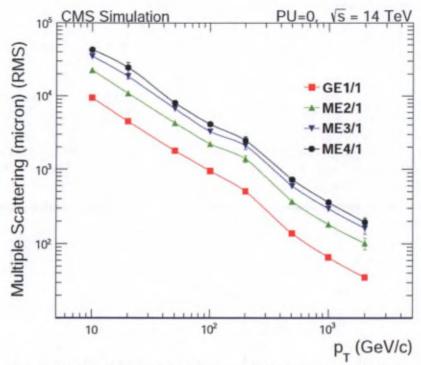

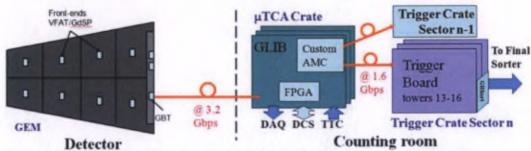

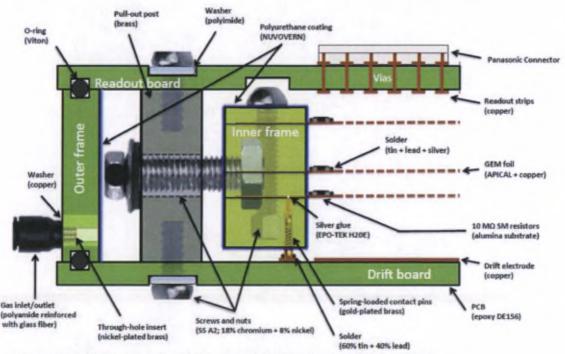

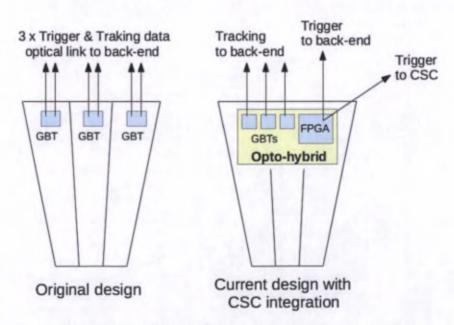

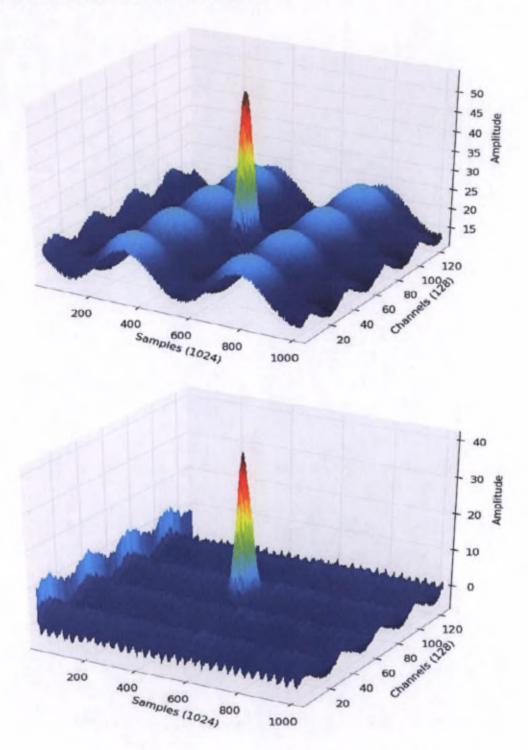

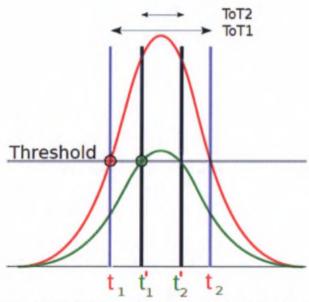

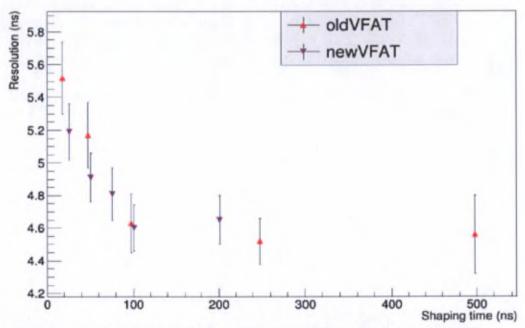

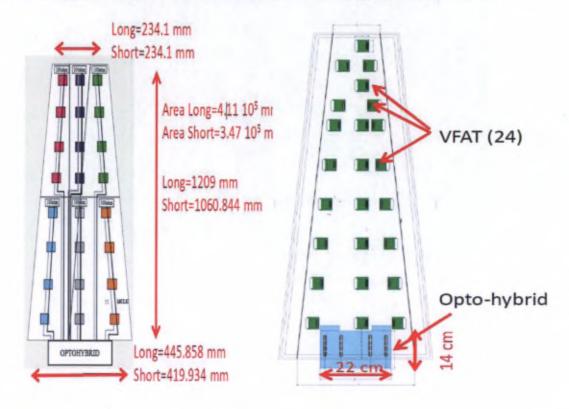

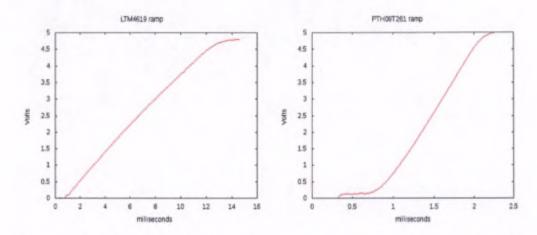

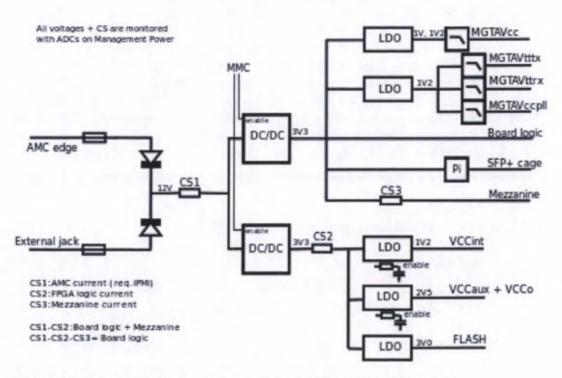

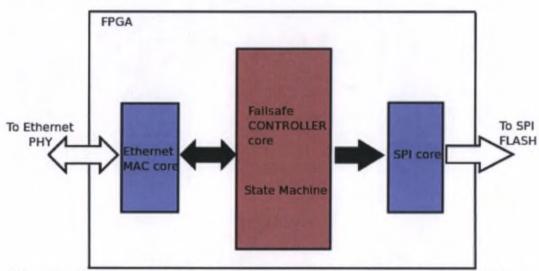

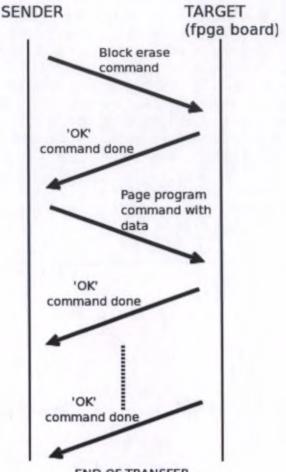

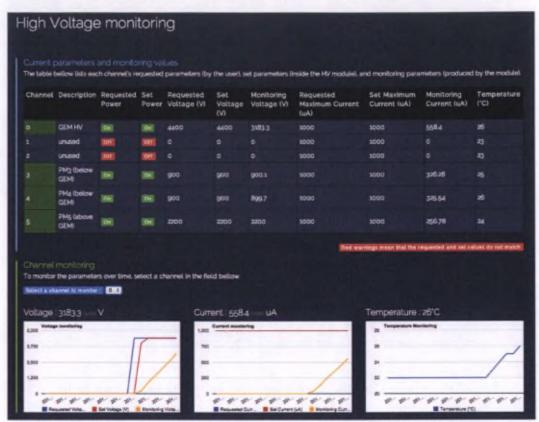

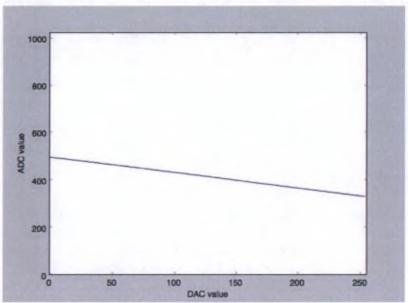

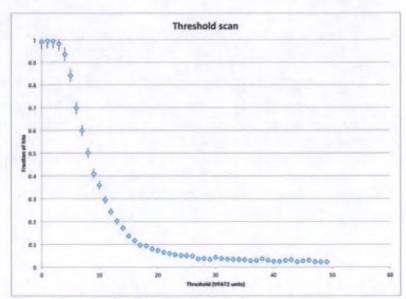

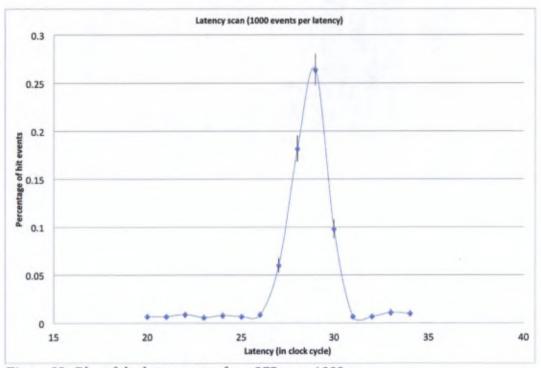

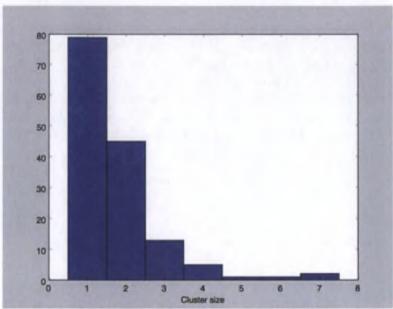

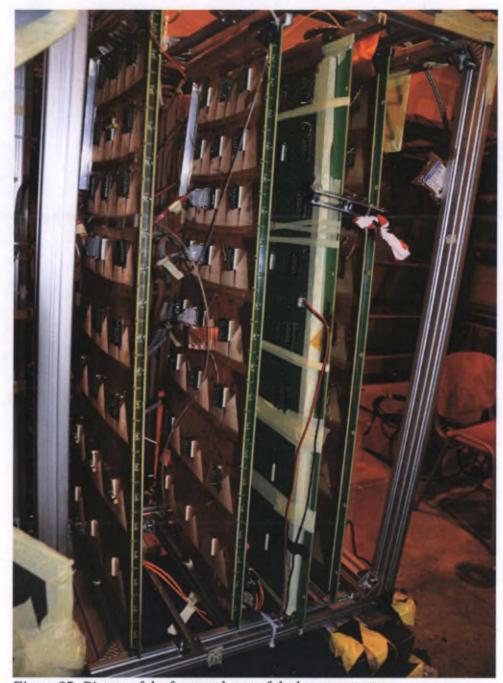

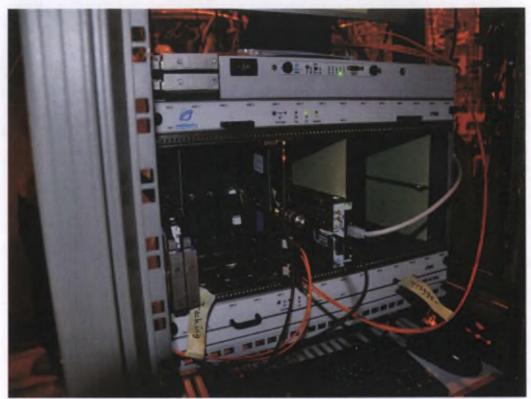

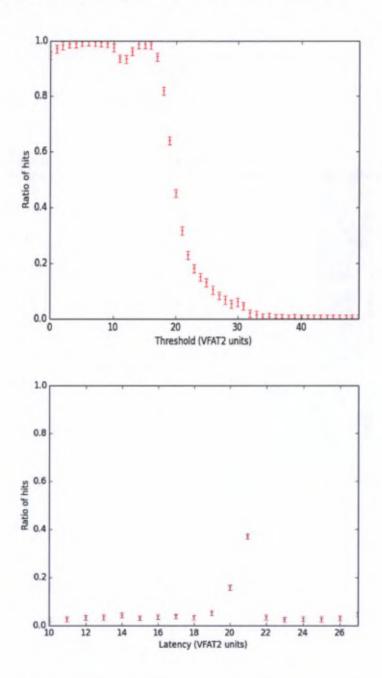

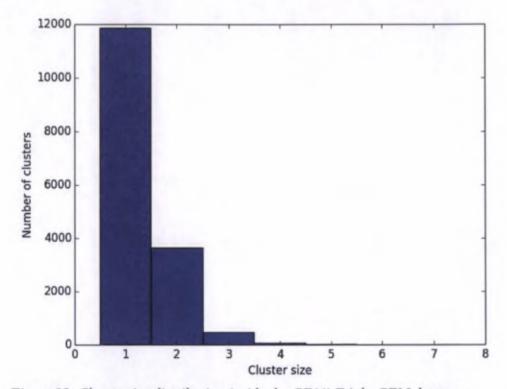

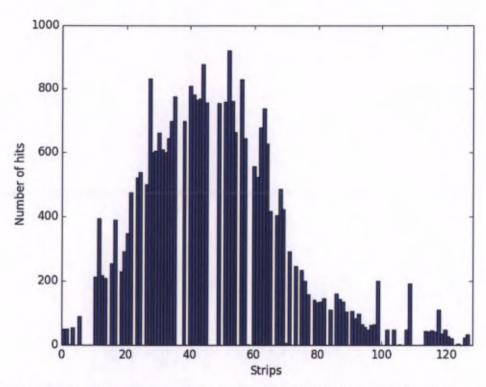

| Sub-detector    | Front-end channels | Number of allocated FED |  |